Cypress Traveo™ II P-DMA 笔记

P-DMA 用于在内存和外设之间传输数据,无需 CPU 参与:CPU 对 P-DMA 进行配置/编程,但实际传输由 P-DMA 控制器完成。主要的设计目标是在有限的平台面积开销下实现 P-DMA 功能。在功能上,P-DMA 控制器类似于通用 DMA 控制器。

一、概述

通道具有关联的优先级,并根据其优先级进行调度。

数据传输由输入触发器启动。 此触发器可能源自传输的源,传输的目的地,CPU软件或另一个SoC组件。 触发器提供活动/睡眠功能,在DeepSleep和Hibernate电源模式下不可用。

数据传输细节由描述符指定。 该描述符指定(除其他事项外):

源地址和目标地址的位置以及传输的大小。

数据传输类型可以是描述符结构中定义的single, 1D, 2D或CRC。 这些类型实质上定义了为源和目标生成的地址序列。 1D和2D传输用于“分散收集”和其他有用的传输操作。

通道的描述符状态被编码为通道的寄存器状态的一部分(而不是描述符的一部分)。 以下寄存器提供通道的描述符状态:

DWx_CH_STRUCTy_CH_CTL – 该寄存器提供通用通道控制信息。

DWx_CH_STRUCTy_CH_CURR_PTR – 该寄存器提供当前描述符所在的存储位置的地址。 软件需要初始化该寄存器。 当从当前描述符前进到描述符列表中的下一个描述符时,硬件将此寄存器设置为当前描述符的下一个描述符指针。

DWx_CH_STRUCTy_CH_IDX – 该寄存器将通道的当前X和Y索引提供到当前描述符中。 软件需要初始化该寄存器。 当从当前描述符前进到描述符列表中的下一个描述符时,硬件会将X和Y索引设置为0。

请注意,通道状态在深度睡眠功耗模式下保持不变。

P-DMA控制器具有活动/睡眠电源模式功能。 如果有任何活动的P-DMA控制器通道正在传输数据,则软件不应启动DeepSleep系统电源模式进入。 请注意,在转换到DeepSleep系统电源模式时,无法捕获活动的通道数据。

二、通道

P-DMA控制器支持由通道管理的多个独立数据传输。 每个通道都通过P-DMA控制器外部的触发器多路复用器连接到特定的系统触发器。

通道优先级。 为通道分配的优先级(DWx_CH_STRUCTy_CH_CTL.PRIO)在0到3之间,其中0为最高优先级,而3为最低优先级。 具有相同优先级的通道构成一个优先级组。 优先级解码确定最高优先级的待处理信道。 该通道的定义如下:

首先确定具有待处理通道的最高优先级组。

在该优先级组中,应用以下“循环”仲裁。 “回合”由该优先级组内的连续通道激活序列组成,没有任何重复。 在回合内,较低的通道索引将具有较高的优先级。 一轮的概念保证了在一个组内,较高的信道索引不会无限期地产生于较低的索引。

通道状态。 在任何给定时间,最多只有一个通道正在主动执行数据传输。 该通道称为活动通道。 通道状态可以是如下四个状态之一:

与触发器关联的数据传输由一个或多个“atomic transfers”或“single transfers”组成。 例如,1D transfer 包含X_COUNT + 1个single transfers 。

通道可能被标记为可抢占(DWx_CH_STRUCTy_CH_CTL.PREEMPTABLE)。 如果可以抢占,并且有较高优先级的待处理通道,则该通道可以在单次传输之间抢占当前通道。

通道具有两个访问控制属性,分别是用于访问控制的SMPU和PPU:

可以将“特权模式”(DWx_CH_STRUCTy_CH_CTL.P)属性设置为特权或用户。

可以将非安全(DWx_CH_STRUCTy_CH_CTL.NS)属性设置为安全或不安全。

与每个通道关联的描述符描述了数据传输。 描述符存储在内存中,DWx_CH_STRUCTy_CH_CURR_PTR 包含与通道“ y”关联的描述符地址。

三、描述符

描述符存储在内存中,并描述数据传输。 该描述符对于P-DMA控制器是只读的。

描述符参数如下:

描述符类型(DESCR_TYPE)– 描述符有四种类型。

Single Transfer

// DST_ADDR is a pointer to an object of type defined by DST_TRANSFER_SIZE

// SRC_ADDR is a pointer to an object of type defined by SRC_TRANSFER_SIZE

// t_DATA_SIZE is the type associated with the DATA_SIZE

DST_ADDR[0] = (t_DATA_SIZE)SRC_ADDR[0];1D Transfer

// DST_ADDR is a pointer to an object of type defined by DST_TRANSFER_SIZE

// SRC_ADDR is a pointer to an object of type defined by SRC_TRANSFER_SIZE

// t_DATA_SIZE is the type associated with the DATA_SIZE

for (X_IDX = 0; X_IDX X_COUNT; X_IDX++)

{

DST_ADDR[X_IDX * DST_X_INCR] = (t_DATA_SIZE)SRC_ADDR[X_IDX * SRC_X_INCR];

}2D Transfer

// DST_ADDR is a pointer to an object of type defined by DST_TRANSFER_SIZE

// SRC_ADDR is a pointer to an object of type defined by SRC_TRANSFER_SIZE

// t_DATA_SIZE is the type associated with the DATA_SIZE

for (Y_IDX = 0; Y_IDX Y_COUNT; Y_IDX++)

{

for (X_IDX = 0; X_IDX X_COUNT; X_IDX++)

{

DST_ADDR[X_IDX * DST_X_INCR + Y_IDX * DST_Y_INCR] = (t_DATA_SIZE)SRC_ADDR[X_IDX * SRC_X_INCR + Y_IDX * SRC_Y_INCR];

}

}CRC Transfer

// DST_ADDR is a pointer to an address location where the calculated CRC is stored.

// SRC_ADDR is a pointer to an object of type defined by SRC_TRANSFER_SIZE

// t_DATA_SIZE is the type associated with the DATA_SIZE

CRC_STATE = CRC_LFSR_CTL;

for (X_IDX = 0; X_IDX X_COUNT; X_IDX++)

{

Update_CRC (CRC_STATE, (t_DATA_SIZE) SRC_ADDR[X_IDX * SRC_X_INCR];

}

DST_ADDR = CRC_STATE;其中,变量X_IDX 和Y_IDX 存储在通道寄存器状态(DWx_CH_STRUCTy_CH_IDX 寄存器)中。参数X_COUNT,Y_COUNT,SRC_X_INCR,SRC_Y_INCR,DST_X_INCR,DST_Y_INCR,SRC_ADDR,DST_ADDR,ZE_SI 和DES 编码器是存储的。

描述符大小 – 描述符的大小取决于其描述符类型。 仅存储相关参数。 例如,一维描述符不包含Y_COUNT,SRC_Y_INCR 和DST_Y_INCR 参数。

传输大小(SRC_TRANSFER_SIZE和DST_TRANSFER_SIZE)– 在数据传输中,源数据被转换为DATA_SIZE指定的类型,并分配给目标。 源类型由SRC_TRANSFER_SIZE确定,目标类型由DST_TRANSFER_SIZE确定。 所有类型都是无符号的。 所有地址计算都根据传输大小使用语义。

描述符链接 – 描述符链接在一起。 DESCR_NEXT_PTR字段包含指向链中下一个描述符的指针。 当通道完成执行当前描述符时,它会执行链中的下一个描述符。 链中的最后一个描述符的DESCR_NEXT_PTR设置为“ 0”(空指针)。 描述符链也称为描述符列表。 可能会有一个循环列表,在这种情况下,执行将无限期继续,直到出现错误或通道或控制器被软件禁用为止。

触发输入类型(TR_IN_TYPE)– 输入触发将启动数据传输,而TR_IN_TYPE定义触发atrigger的操作。

Table 7-3. P-DMA Trigger-in Types

触发输出类型(TR_OUT_TYPE)– 定义何时生成输出触发。

Table 7-4. P-DMA Trigger-out Types

中断类型(INTR_TYPE)– 定义何时生成完成中断。

Table 7-5. P-DMA Interrupt Types

等待停用(WAIT_FOR_DEACT)– 指定P-DMA控制器在完成与当前触发器相对应的数据传输后是否应等待停用输入触发器。 该字段用于对电平敏感的触发器,以便为触发代理提供足够的时间来停用触发器。 指定的等待时间可以为0,最多四个周期,最多16个周期或不确定的。对脉冲敏感的触发器应将此字段设置为0。

四、中断

P-DMA可以在完成条件和各种错误条件下生成中断。

INTR_TYPE描述符控件定义何时激活完成条件(COMPLETION)。

错误条件包括SRC_BUS_ERROR,DST_BUS_ERROR,SRC_MISAL,DST_MISAL,CURR_PTR_NULL,ACTIVE_CH_DISABLED和DESCR_BUS_ERROR。

中断源存储在描述符中定义的DWx_CH_STRUCTy_CH_STATUS.INTR_CAUSE.INTR_TYPE 中,用于控制何时生成完成中断。 每个通道具有四个与中断有关的寄存器。

DWx_CH_STRUCTy_INTR – 每个通道都有一个中断请求寄存器。 当检测到中断事件(完成或错误)时,位0设置为1。 软件可以通过写入该位来清除此错误。

DWx_CH_STRUCTy_INTR_SET – 每个通道都有一个中断设置寄存器。 软件可以向该寄存器写入1来设置相应的DWx_CH_STRUCTy_INTR寄存器。

DWx_CH_STRUCTy_INTR_MASK – 每个通道都有一个中断屏蔽寄存器。 通过向该寄存器写入1来启用相应的中断。

DWx_CH_STRUCTy_INTR_MASKED – 每个通道都有一个已屏蔽中断寄存器。 读取时,该寄存器反映了中断请求和屏蔽寄存器之间的按位与。

P-DMA是有功功率模式外设; 这意味着,它使用活动功能中断。 因此,DWx_CH_STRUCTy_INTR和DWx_CH_STRUCTy_INTR_SET在深度睡眠功耗模式下不保留(保留DWx_CH_STRUCTy_INTR_MASK)。

五、P-DMA Controller Status Registers

控制器DWx_STATUS0寄存器包含以下信息。

DWx_STATUS0.ACTIVE - 存在活动通道,否/是

DWx_STATUS0.P - 活动通道访问控制,用户/特权

DWx_STATUS0.NS - 活动通道访问控制,安全/不安全

DWx_STATUS0.B - 有效通道访问控制,不可缓冲/可缓冲

DWx_STATUS0.PC - 有效通道保护上下文

DWx_STATUS0.CH_IDX - 有效通道索引(如果有有效通道)

DWx_STATUS0.PRIO - 有效通道优先级

DWx_STATUS0.PREEMPTABLE - 有效通道可抢占

DWx_STATUS0.STATE - 不活动,正在加载描述符,正在加载数据元素,正在存储数据元素或等待触发器停用中的一种

DWx_CH_STRUCTy_CH_STATUS.PENDING 寄存器位指定通道当前是否处于挂起状态。

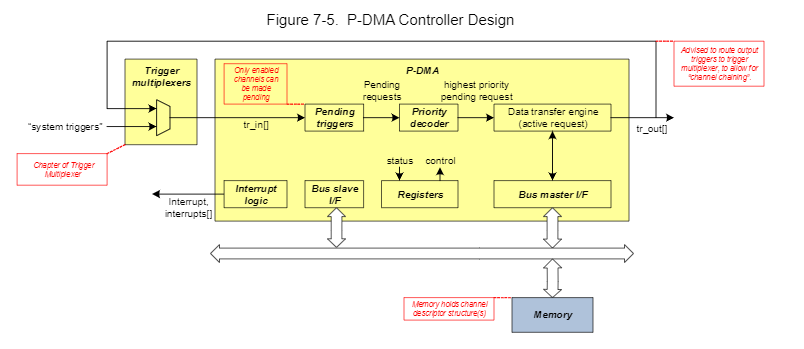

六、P-DMA Controller Design

下图概述了P-DMA控制器的设计。

在此图中,P-DMA控制器的输出触发是作为组件输入触发的反馈。 该反馈是在组件外部完成的。